高電圧増幅器

GBコンデンサによる高電圧増幅器の性能改善 その2(3段接続)

出力段mosFETを正負各3段で構成した

GBコンデンサ

の働きを説明します

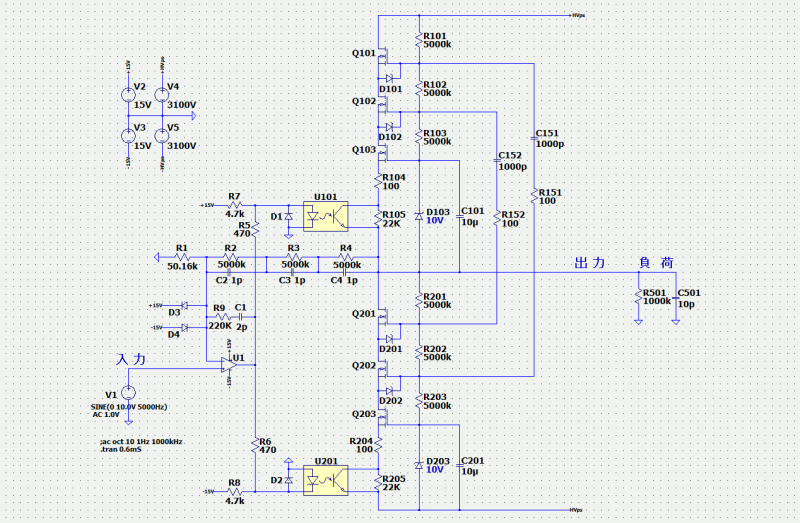

Fig 33-1

mosFET正負各3段ので構成した±3kV出力の高電圧増幅器です。

Q101のゲートとQ202のゲート間にGBコンデンサC151が、また、Q102のゲートとQ201のゲート間にGBコンデンサC152が設けられています。

任意のnについて

mosFETの接続段数をn段に増やし、GBコンデンサを(n-1)個設けることで、更に高電圧化、高耐圧化することが出来ます。

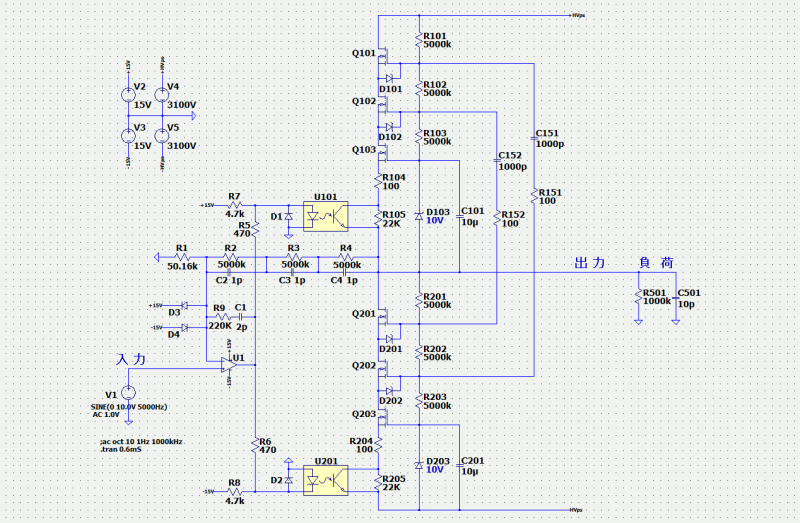

Q101のゲートとQ202のゲート間にGBコンデンサC151が、また、Q102のゲートとQ201のゲート間にGBコンデンサC152が設けられています。

任意のnについて

mosFETの接続段数をn段に増やし、GBコンデンサを(n-1)個設けることで、更に高電圧化、高耐圧化することが出来ます。

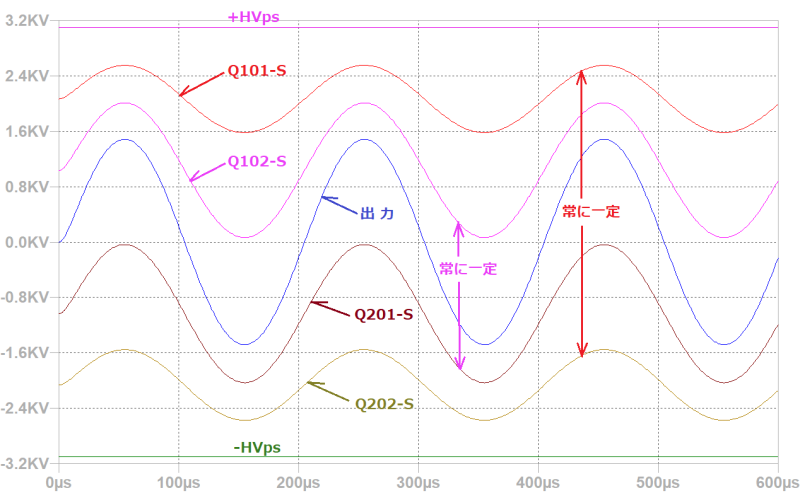

Fig 33-2

Q101-S:Q101のソース波形 Q102-S:Q102のソース波形

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

5kHz、±5Vpk正弦波入力に対する±1.5kVpk出力時の各mosFET ソースと出力の波形です。

正側mosFET Q101のソース電位Vs101と負側mosFET Q202のソース電位Vs202との電位差(Vs101-Vs202)は、常に一定値aを保っています。

正側mosFET Q102のソース電位Vs102と負側mosFET Q201のソース電位Vs201との電位差(Vs102-Vs201)は、常に一定値bを保っています。

ここに、一定値aと一定値bは異なりa≒2bの関係にあります。

従って、GBコンデンサC151とC152に要求される耐圧は異なります。

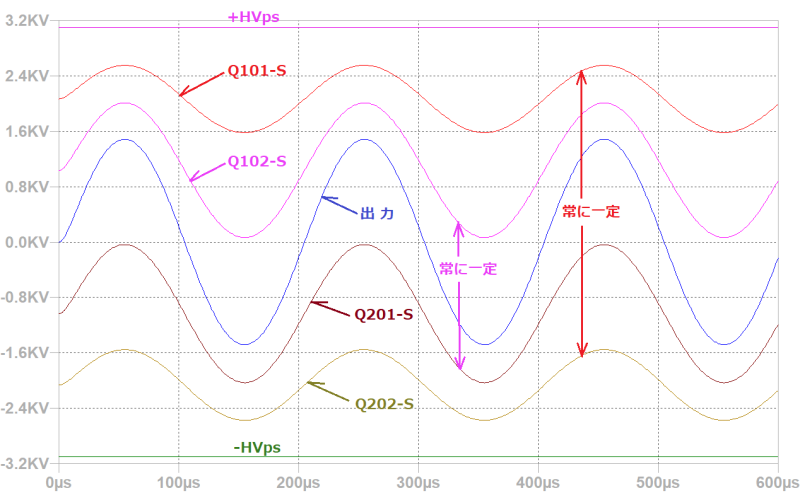

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

5kHz、±5Vpk正弦波入力に対する±1.5kVpk出力時の各mosFET ソースと出力の波形です。

正側mosFET Q101のソース電位Vs101と負側mosFET Q202のソース電位Vs202との電位差(Vs101-Vs202)は、常に一定値aを保っています。

正側mosFET Q102のソース電位Vs102と負側mosFET Q201のソース電位Vs201との電位差(Vs102-Vs201)は、常に一定値bを保っています。

ここに、一定値aと一定値bは異なりa≒2bの関係にあります。

従って、GBコンデンサC151とC152に要求される耐圧は異なります。

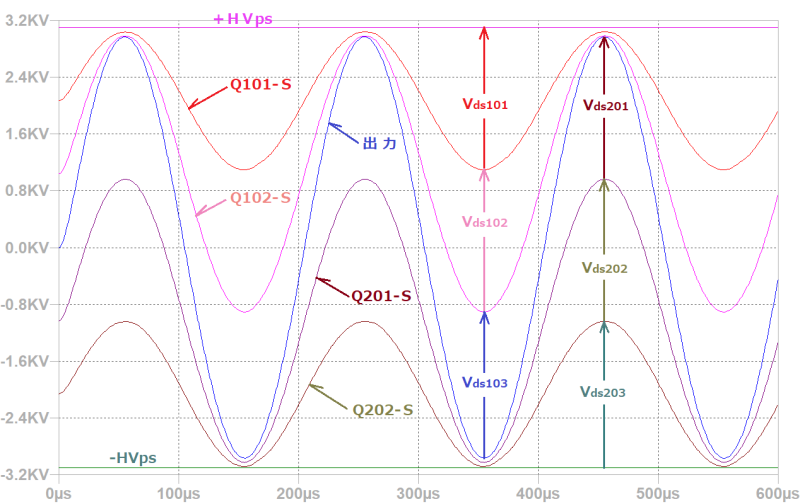

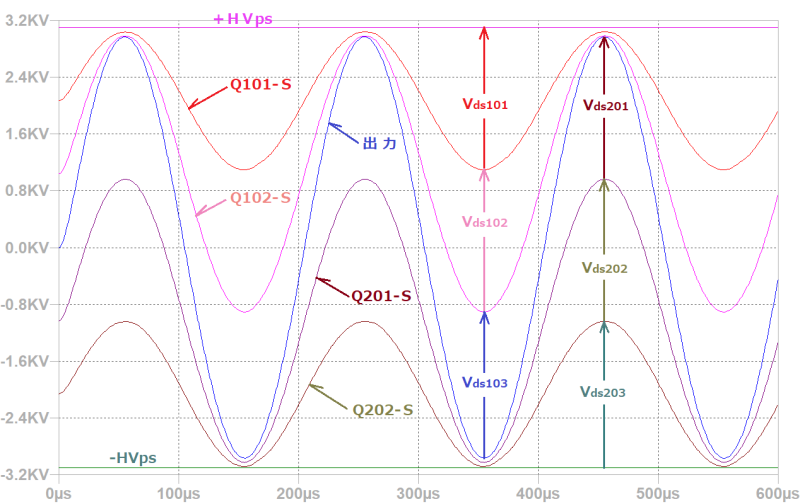

Fig 33-3

Q101-S:Q101のソース波形 Q102-S:Q102のソース波形 Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

Vds101:Q101のVds Vds102:Q102のVds Vds103:Q103のVds

Vds201:Q201のVds Vds202:Q202のVds Vds203:Q203のVds

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

5kHz、±10Vpk正弦波入力に対する±3kVpk出力時の各mosFET ソースと出力の波形です。

正側mosFET Q101、Q102、Q103のドレインーソース間電圧Vds101、Vds102、Vds103が均等に配分(バランス)されています。

Vds101≒Vds102≒Vds103=Vds1は、入力信号に応じて変化します。

負側mosFET Q201、Q202、Q203のドレインーソース間電圧Vds201、Vds202、Vds203も均等に配分(バランス)されています。

Vds201≒Vds202≒Vds203=Vds2も、入力信号に応じて変化します。

このように正側、負側で個々のmosFETに加わる電圧が崩れることなく均等にバランスしています。

各mosFETは数kVの電位が変化しているので、高電圧増幅回路をシールドケースに収めるときのケース間とのストレー容量には注意が必要です。

(通常はGNDに落とされている)シールドケースとmosFET間のストレー容量が悪影響して、特性を劣化させます。

とくに出力に近いQ102(Q201)が高圧電源側に近いQ101(Q202)より2倍電位変動(振幅)があるので、その影響が2倍になります。

これらのことは、mosFETのみならず、その周辺(C,R)部品についても同様です。

Q103は出力に近く、他のmosFETに比べて電位変動が大きいですが、低インピーダンスでドライブされているので影響は比較的軽微です。

Vds101:Q101のVds Vds102:Q102のVds Vds103:Q103のVds

Vds201:Q201のVds Vds202:Q202のVds Vds203:Q203のVds

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

5kHz、±10Vpk正弦波入力に対する±3kVpk出力時の各mosFET ソースと出力の波形です。

正側mosFET Q101、Q102、Q103のドレインーソース間電圧Vds101、Vds102、Vds103が均等に配分(バランス)されています。

Vds101≒Vds102≒Vds103=Vds1は、入力信号に応じて変化します。

負側mosFET Q201、Q202、Q203のドレインーソース間電圧Vds201、Vds202、Vds203も均等に配分(バランス)されています。

Vds201≒Vds202≒Vds203=Vds2も、入力信号に応じて変化します。

このように正側、負側で個々のmosFETに加わる電圧が崩れることなく均等にバランスしています。

各mosFETは数kVの電位が変化しているので、高電圧増幅回路をシールドケースに収めるときのケース間とのストレー容量には注意が必要です。

(通常はGNDに落とされている)シールドケースとmosFET間のストレー容量が悪影響して、特性を劣化させます。

とくに出力に近いQ102(Q201)が高圧電源側に近いQ101(Q202)より2倍電位変動(振幅)があるので、その影響が2倍になります。

これらのことは、mosFETのみならず、その周辺(C,R)部品についても同様です。

Q103は出力に近く、他のmosFETに比べて電位変動が大きいですが、低インピーダンスでドライブされているので影響は比較的軽微です。