高電圧増幅器

高圧電源立ち上げ時の電圧バランス

不安定な高圧電源の立上げ時、各mosFETに加わる電圧バランスが崩れて

いないかを確認します

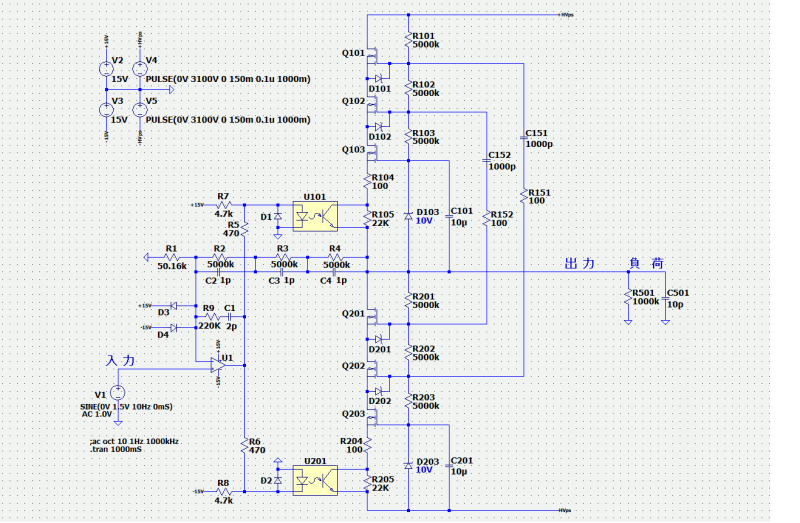

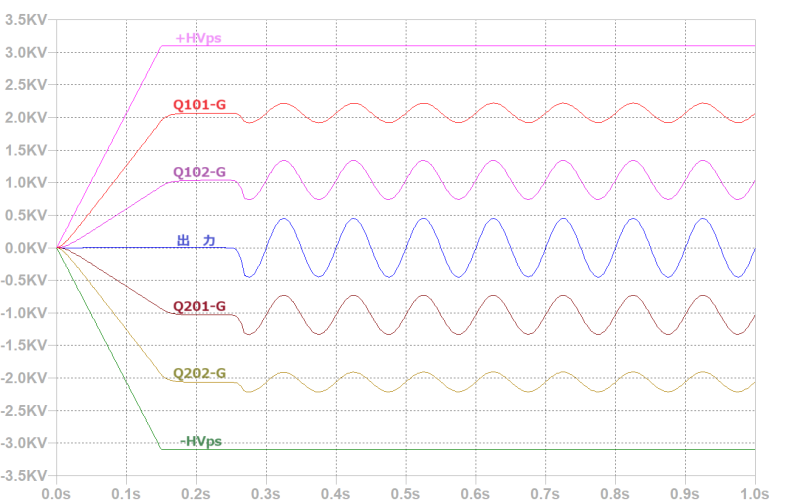

Fig 35-1

Fig33-1の回路と同じですが、±HVps高圧電源の立上がりをなだらかにしています。

電源ON時、±15V電源は、一般的に高圧電源より立上がりが早いので、t=0mSで立上がっているものとしています。

また10Hz、±1.5Vpkの正弦波入力信号もt=0mSから印加されています。

電源ON時、±15V電源は、一般的に高圧電源より立上がりが早いので、t=0mSで立上がっているものとしています。

また10Hz、±1.5Vpkの正弦波入力信号もt=0mSから印加されています。

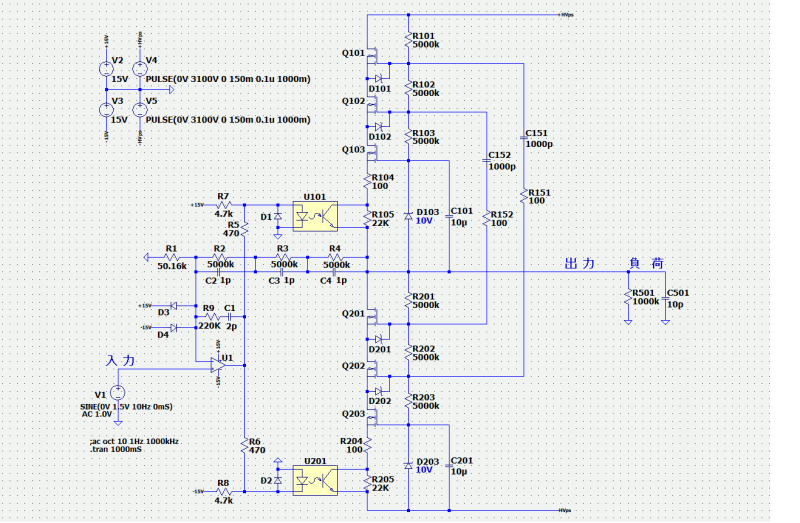

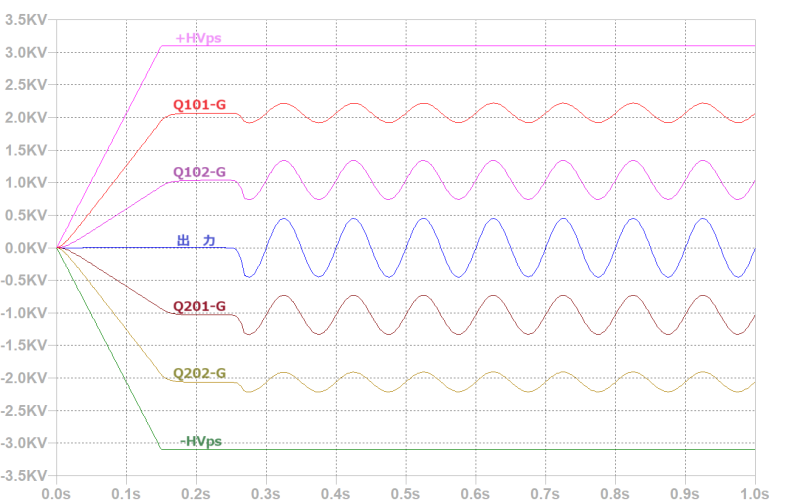

Fig 35-2

Q101-S:Q101のソース波形 Q102-S:Q102のソース波形

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が30mSで立上がったときの各mosFETのゲートと出力の応答波形です。

(実際には30mSほどの短時間で高圧電源を立上げることは、難しい。)

出力には高圧電源が立上がってから更に200mSほど遅れてから波形が現れています。

正弦波出力波形が現れる手前の約50mS間で、出力が多少不安定となっています。

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が30mSで立上がったときの各mosFETのゲートと出力の応答波形です。

(実際には30mSほどの短時間で高圧電源を立上げることは、難しい。)

出力には高圧電源が立上がってから更に200mSほど遅れてから波形が現れています。

正弦波出力波形が現れる手前の約50mS間で、出力が多少不安定となっています。

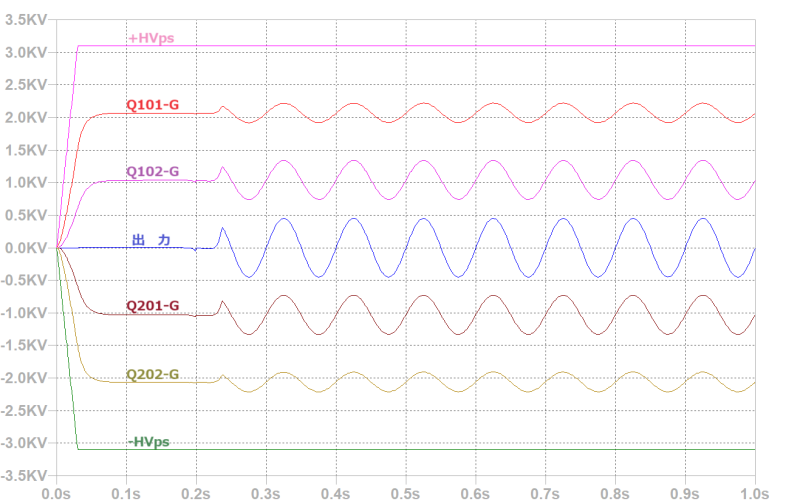

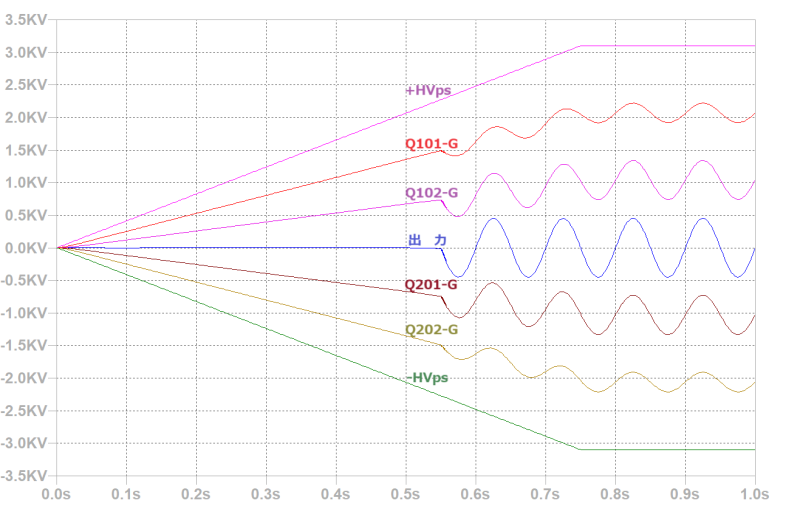

Fig 35-3

Q101-S:Q101のソース波形 Q102-S:Q102のソース波形

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が150mSで立上がったときの各mosFETのゲートと出力の応答波形です。

出力には高圧電源が立上がってから更に100mSほど遅れてから波形が現れています。

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が150mSで立上がったときの各mosFETのゲートと出力の応答波形です。

出力には高圧電源が立上がってから更に100mSほど遅れてから波形が現れています。

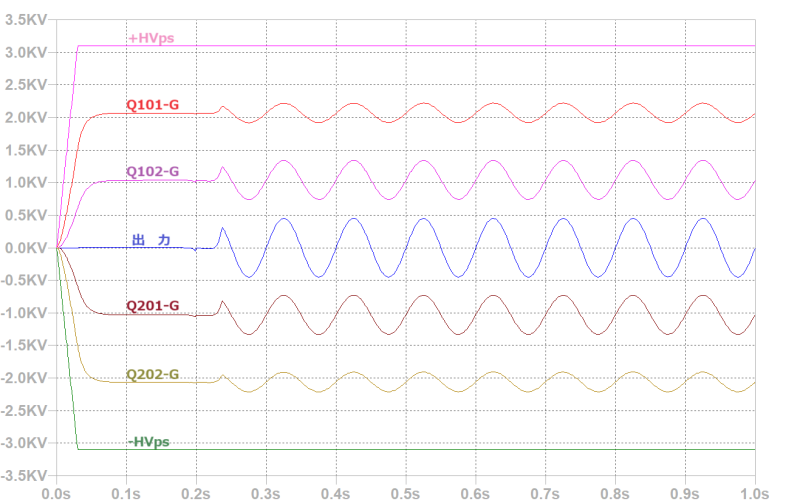

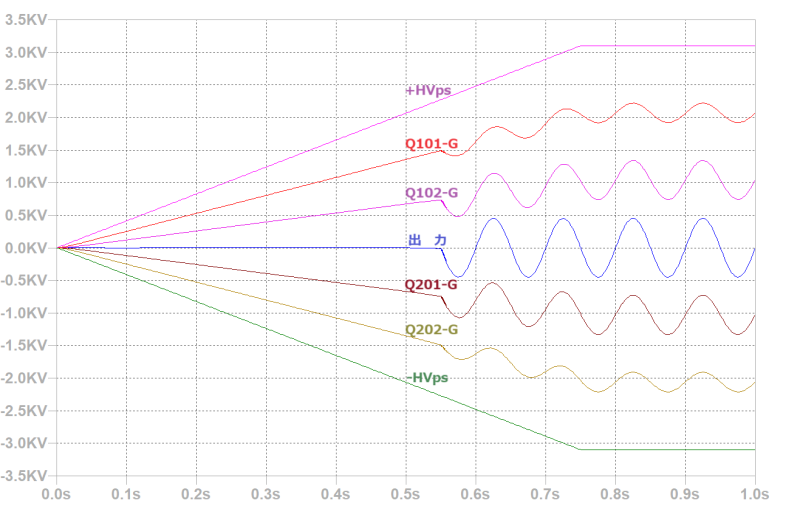

Fig 35-4

Q101-S:Q101のソース波形 Q102-S:Q102のソース波形

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が750mSで立上がったときの各mosFETのゲートと出力の応答波形です。

立上がりが遅いので、出力には高圧電源が完全に立上がるより約200mS手前から波形が現れています。

正弦波出力波形が現れる前後の約50mS間で、出力が多少不安定となっています(発信と似た現象)。

高圧電源の立上がり時間が30mS(Fig35-2)、150mS(Fig35-3)、750mS(Fig35-4)の何れにおいても

±HVps高圧電源が安定するまでの立上がり時に、特定のmosFETに電圧が過大に印加されることなく均等にバランスが保たれています。

Q201-S:Q201のソース波形 Q202-S:Q202のソース波形

+HVps :+3100V高圧電源 -HVps :-3100V高圧電源

±HVps高圧電源が750mSで立上がったときの各mosFETのゲートと出力の応答波形です。

立上がりが遅いので、出力には高圧電源が完全に立上がるより約200mS手前から波形が現れています。

正弦波出力波形が現れる前後の約50mS間で、出力が多少不安定となっています(発信と似た現象)。

高圧電源の立上がり時間が30mS(Fig35-2)、150mS(Fig35-3)、750mS(Fig35-4)の何れにおいても

±HVps高圧電源が安定するまでの立上がり時に、特定のmosFETに電圧が過大に印加されることなく均等にバランスが保たれています。