高電圧増幅器

ブースターアンプ部の静止電流

高圧電源の容量は限られています

出力ワット数が同じであれば、高電圧化すればするほど、出力電流容量は

小さくなります

ブースタ-アンプ部の多段mosFETに流れる静止電流を抑えて高効率化を検討

します

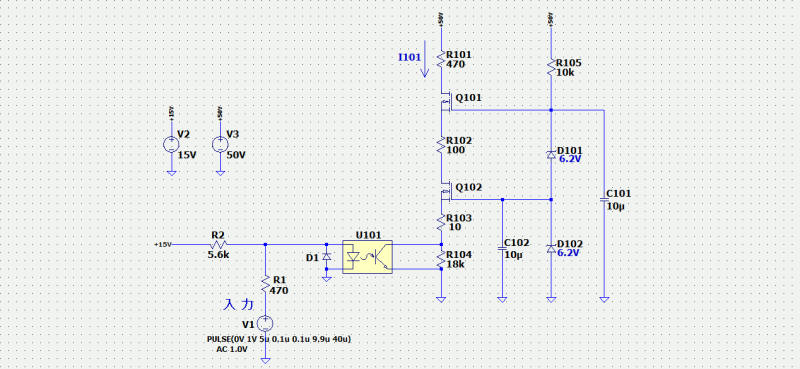

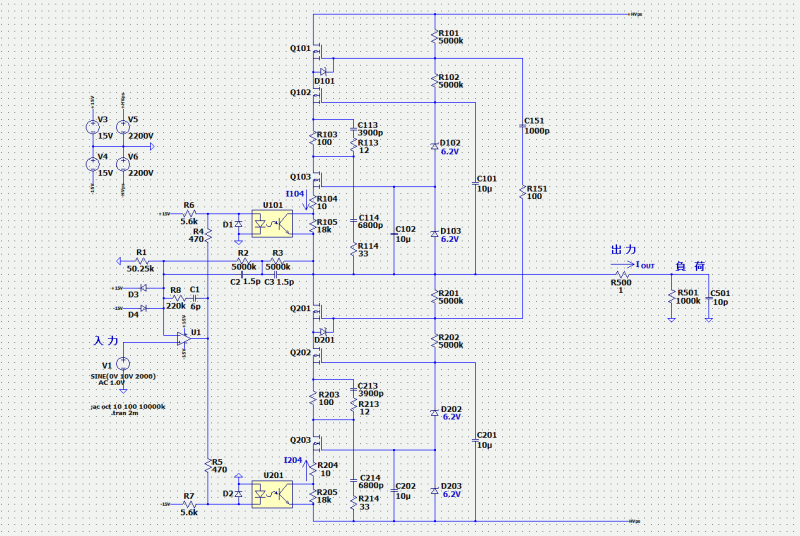

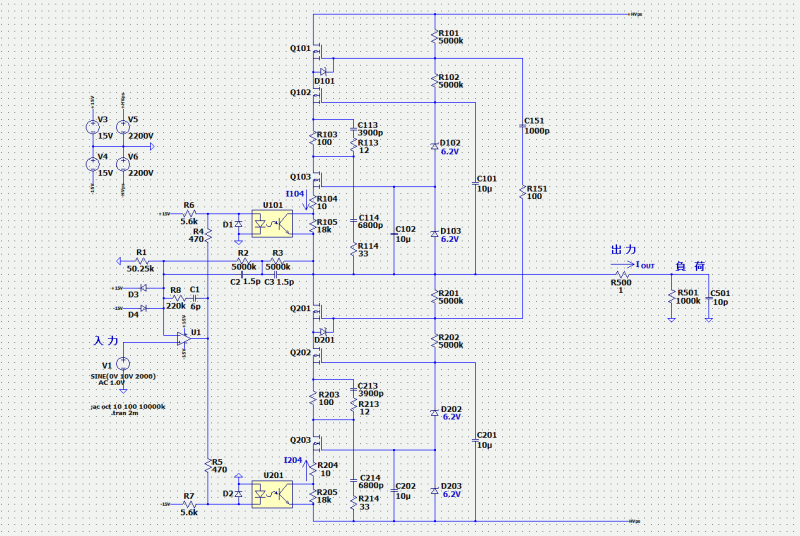

Fig 53-1

Fig51-3の回路における抵抗R2の値を4.7kΩから5.6kΩに大きくし、抵抗R101に流れる静止電流I101を抑えた回路です。

R2は、ゼロクロス歪を抑えるために必要な抵抗です。

0V入力時に+15V電源からR2を通してフォト・カプラーU101にバイアス電流を供給しています。

R2は、ゼロクロス歪を抑えるために必要な抵抗です。

0V入力時に+15V電源からR2を通してフォト・カプラーU101にバイアス電流を供給しています。

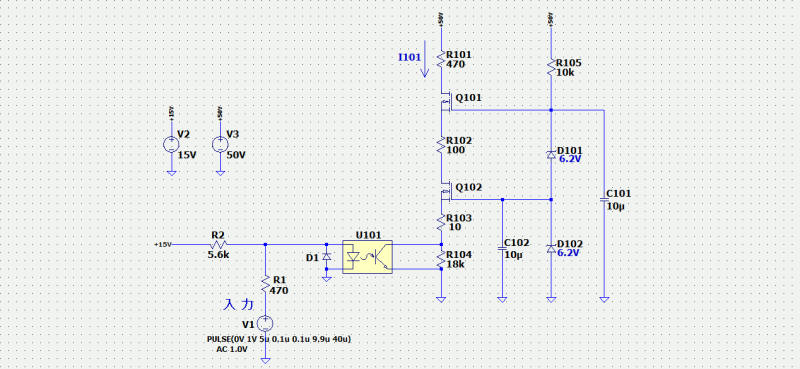

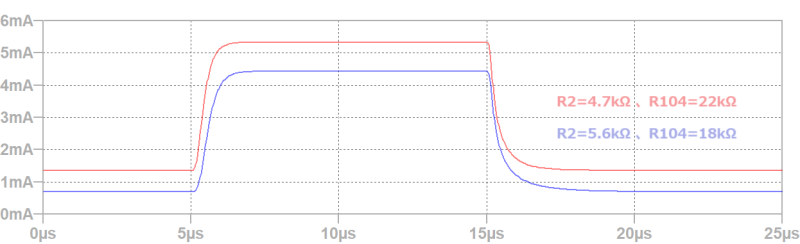

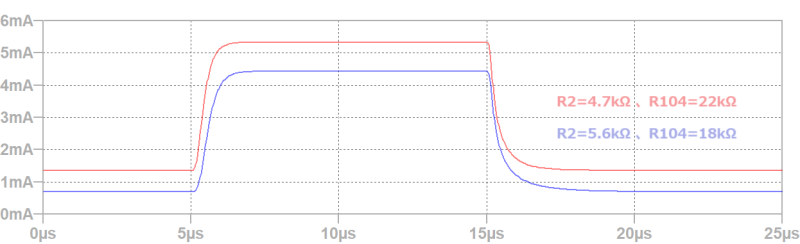

Fig 53-2

0V/1Vpkパルス入力に対する抵抗R101に流れる電流I101の応答波形です。

R2の抵抗値を4.7kΩから5.6kΩに上げて、0V入力時の静止電流I101を750uAに抑えています。

0V/1Vpkパルス入力に対する抵抗R101に流れる電流I101の応答波形です。

R2の抵抗値を4.7kΩから5.6kΩに上げて、0V入力時の静止電流I101を750uAに抑えています。

Fig 53-3

抵抗R6、R7を5.6kΩに上げQ101〜Q103、Q201〜Q203に流れる静止電流を下げ

また、静止電流を小さくしたためC1=6pF、C2=C3=1.5pFとし、高電圧増幅器としての帯域を21kHzに狭めています。

また、静止電流を小さくしたためC1=6pF、C2=C3=1.5pFとし、高電圧増幅器としての帯域を21kHzに狭めています。

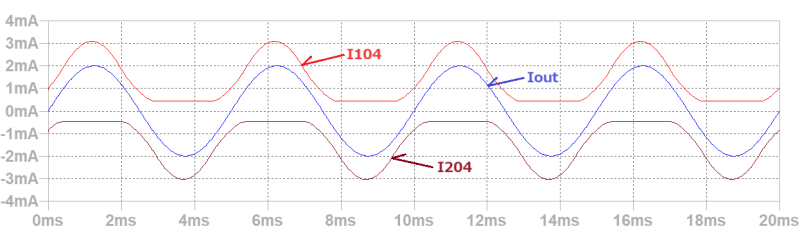

Fig 53-4

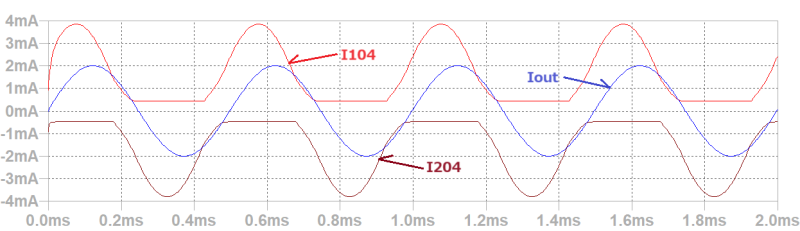

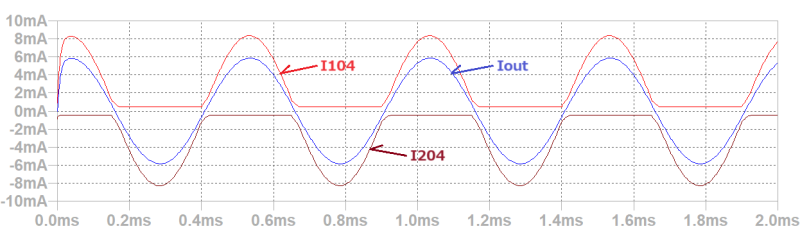

赤:抵抗R104に流れる電流I104 青:抵抗R500に流れる出力電流Iout 茶:抵抗R204に流れる電流I204

負荷容量C501=10pにおける±10Vpk、200Hz正弦波入力に対するI104、I204、Ioutの電流波形です。

200Hzであれば、I104、I204とIoutは、ほぼ同位相となります。

尚、I104の最少電流(0V入力時と同じ)は約400uAに抑えられています。

同様に、I204の最少電流(0V入力時と同じ)も約-400uAに抑えられています。

負荷容量C501=10pにおける±10Vpk、200Hz正弦波入力に対するI104、I204、Ioutの電流波形です。

200Hzであれば、I104、I204とIoutは、ほぼ同位相となります。

尚、I104の最少電流(0V入力時と同じ)は約400uAに抑えられています。

同様に、I204の最少電流(0V入力時と同じ)も約-400uAに抑えられています。

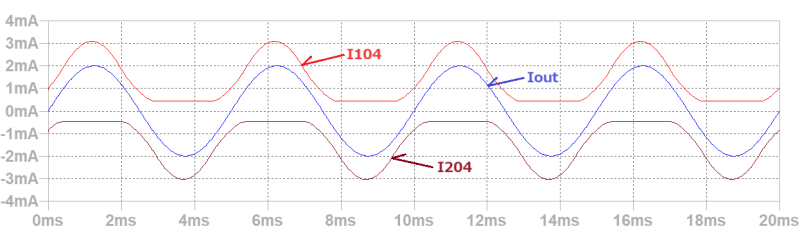

Fig 53-5

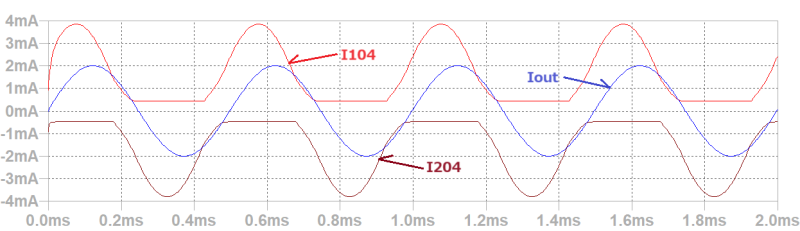

赤:抵抗R104に流れる電流I104 青:抵抗R500に流れる出力電流Iout 茶:抵抗R204に流れる電流I204

負荷容量C501=10pにおける±10Vpk、2kHz正弦波入力に対するI104、I204、Ioutの電流波形です。

2kHzに上がると、I104、I204の位相よりIoutの位相が、このように遅れています。

負荷容量C501=10pにおける±10Vpk、2kHz正弦波入力に対するI104、I204、Ioutの電流波形です。

2kHzに上がると、I104、I204の位相よりIoutの位相が、このように遅れています。

Fig 53-6

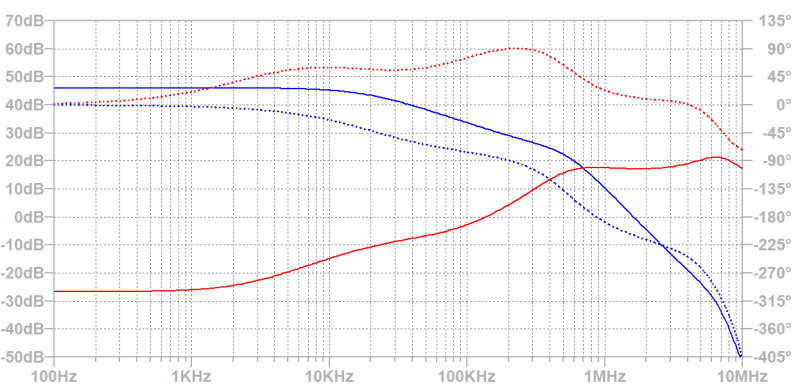

実線:振幅 / 点線:位相

赤 :OP AmpU1出力 青 :出力

Fig53-3の周波数特性です。

これから分かるように、周波数2kHzで赤のOP AmpU1出力は青の高電圧増幅器の出力より位相が進んでいます。

この特性から、Fig53-5におけるI104、I204の位相(これらはOP AmpU1出力と同相)とIoutとの間に位相差が生じている理由が分かります。

赤 :OP AmpU1出力 青 :出力

Fig53-3の周波数特性です。

これから分かるように、周波数2kHzで赤のOP AmpU1出力は青の高電圧増幅器の出力より位相が進んでいます。

この特性から、Fig53-5におけるI104、I204の位相(これらはOP AmpU1出力と同相)とIoutとの間に位相差が生じている理由が分かります。

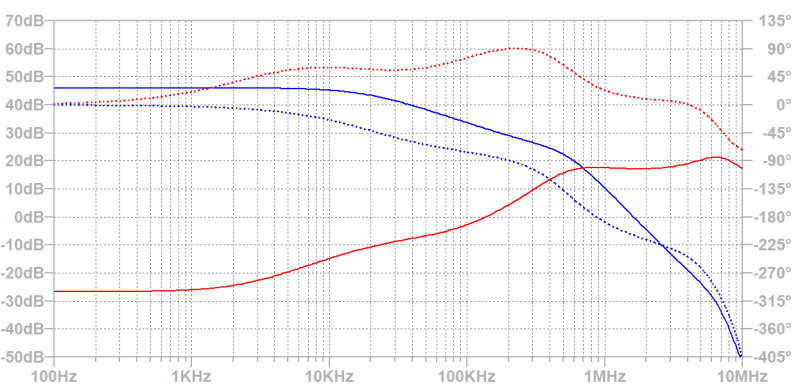

赤:抵抗R104に流れる電流I104 青:抵抗R500に流れる出力電流Iout 茶:抵抗R204に流れる電流I204

負荷容量C501=220pにおける±10Vpk、2kHz正弦波入力に対するI104、I204、Ioutの電流波形です。

負荷容量が大きくなり出力電流Ioutの位相が遅れるため、I104、I204の位相に近づいています。

負荷容量C501=220pにおける±10Vpk、2kHz正弦波入力に対するI104、I204、Ioutの電流波形です。

負荷容量が大きくなり出力電流Ioutの位相が遅れるため、I104、I204の位相に近づいています。