高電圧増幅器

mosFETの電流波形

正負各2段のmosFETで構成された高電圧増幅器の正側mosFETの

各ノードに流れる電流波形を確認します

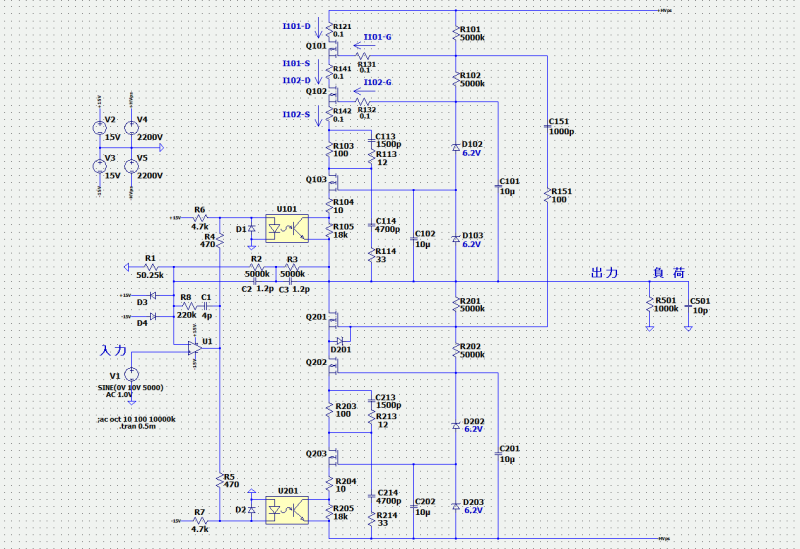

Fig 54-1

mosFET Q101、Q102の各ノードに流れる電流の様子を確認するために0.1Ωの抵抗R121、R131、R132、R141、R142を入れています。

また、ここではQ101のゲートを保護するためのツェナーダイオードは省略しています。

また、ここではQ101のゲートを保護するためのツェナーダイオードは省略しています。

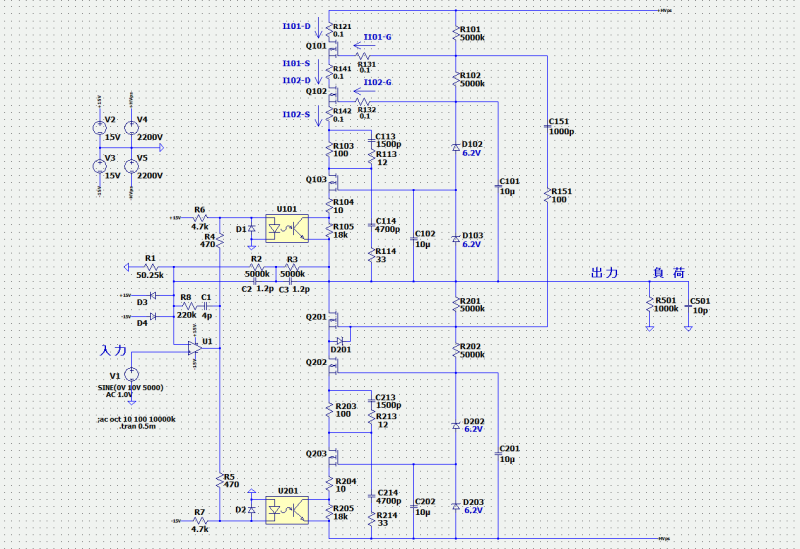

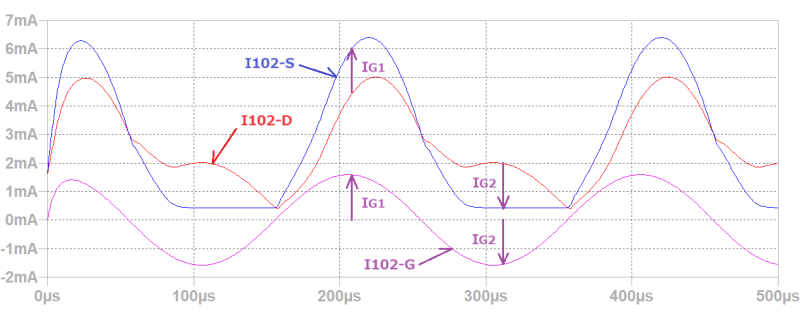

Fig 54-2

赤:Q102のドレイン電流I102-D 青:Q102のソース電流I102-S 紫:Q102のゲート電流I102-G

5kHz、±10Vpk正弦波入力に対するmosFET Q102の各ノードの電流波形です。

ゲート電流I102-Gが正の区間では、ソース電流I102-Sがドレイン電流I102-Dより大きくなっています。

これは、図のようにゲート電流IG1がドレイン電流I102-Dに加わりソース電流I102-Sになっていることを示しています。

つまり、ゲート電流が正の区間では、GBコンデンサC151から供給される電流IG1(I102-G)がドレイン電流に加わりソース電流となります。

ゲート電流I102-Gが負の区間では、ソース電流I102-Sがドレイン電流I102-Dより小さくなっています。

これは、図のようにゲート電流IG2(I102-G)をドレイン電流I102-Dから差し引いたものがソース電流I102-Sになっていることを示しています。

つまり、ゲート電流が負の区間では、GBコンデンサC151へのチャージ電流IG2(I102-G)とソース電流I102-Sがドレイン電流I102-Dから供給されています。

ゲート電流が負の区間でドレイン電流が0まで下がらず小さなピークが現れているのは、GBコンデンサC151にチャージしているためです。

GBコンデンサC151にチャージされた電荷は、ゲート電流I102-Gが正のときに必要とされるソース電流として戻されていることになります。

負側のQ202も同様です。

5kHz、±10Vpk正弦波入力に対するmosFET Q102の各ノードの電流波形です。

ゲート電流I102-Gが正の区間では、ソース電流I102-Sがドレイン電流I102-Dより大きくなっています。

これは、図のようにゲート電流IG1がドレイン電流I102-Dに加わりソース電流I102-Sになっていることを示しています。

つまり、ゲート電流が正の区間では、GBコンデンサC151から供給される電流IG1(I102-G)がドレイン電流に加わりソース電流となります。

ゲート電流I102-Gが負の区間では、ソース電流I102-Sがドレイン電流I102-Dより小さくなっています。

これは、図のようにゲート電流IG2(I102-G)をドレイン電流I102-Dから差し引いたものがソース電流I102-Sになっていることを示しています。

つまり、ゲート電流が負の区間では、GBコンデンサC151へのチャージ電流IG2(I102-G)とソース電流I102-Sがドレイン電流I102-Dから供給されています。

ゲート電流が負の区間でドレイン電流が0まで下がらず小さなピークが現れているのは、GBコンデンサC151にチャージしているためです。

GBコンデンサC151にチャージされた電荷は、ゲート電流I102-Gが正のときに必要とされるソース電流として戻されていることになります。

負側のQ202も同様です。

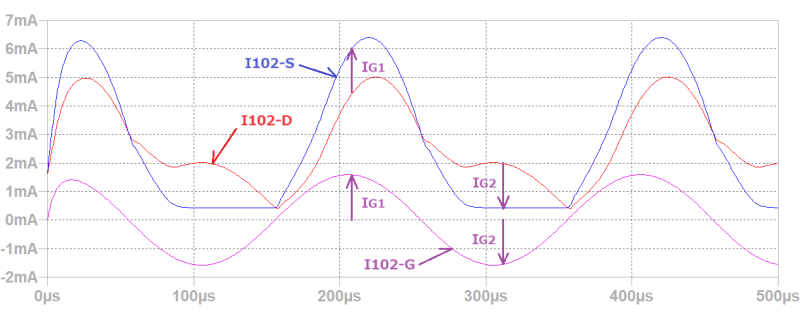

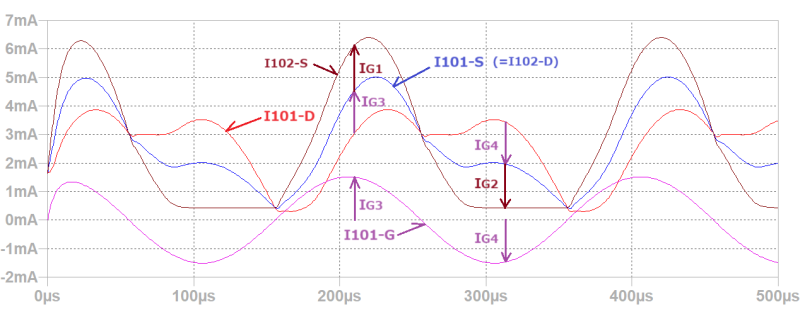

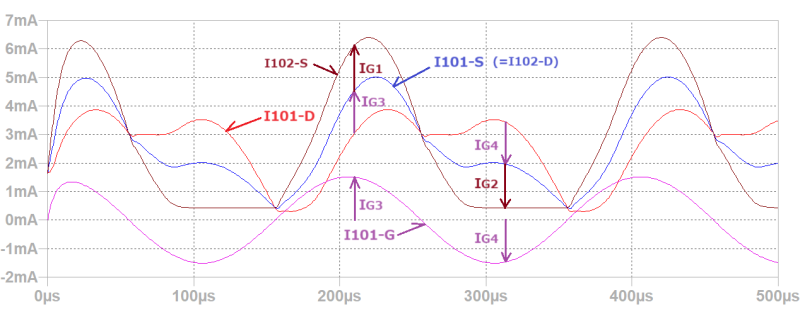

Fig 54-3

赤:Q101のドレイン電流I101-D 青:Q101のソース電流I101-S 紫:Q101のゲート電流I101-G

(青:Q102のドレイン電流I102-D) 茶:Q102のソース電流I102-S

5kHz、±10Vpk正弦波入力に対するmosFET Q101の各ノードの電流波形です。Q102のソース電流波形も加えてあります。

ゲート電流I101-Gが正の区間では、ソース電流I101-Sがドレイン電流I101-Dより大きくなっています。

これは、図のようにゲート電流IG3(I101-G)がドレイン電流I101-Dに加わりソース電流I101-Sになっていることを示しています。

つまり、ゲート電流が正の区間では、電流IG3(I101-G)がドレイン電流に加わりソース電流となります。

ゲート電流I101-Gが負の区間では、ソース電流I101-Sがドレイン電流I101-Dより小さくなっています。

これは、図のようにゲート電流IG4(I101-G)をドレイン電流I101-Dから差し引いたものがソース電流I101-Sになっていることを示しています。

つまり、ゲート電流が負の区間では、電流IG4(I101-G)とソース電流I101-Sはドレイン電流I101-Dから供給されています。

ゲート電流が負の区間でドレイン電流I101-Dが0まで下がらず(I102-Dよりも2倍大きな)ピークが現れています。

この回路は正負各2段のmosFETで構成されていますが、更に段数が多い場合、正側では高圧電源側に近いmosFETほど、そのピークが大きくなります。

負側のQ201も同様です。

(青:Q102のドレイン電流I102-D) 茶:Q102のソース電流I102-S

5kHz、±10Vpk正弦波入力に対するmosFET Q101の各ノードの電流波形です。Q102のソース電流波形も加えてあります。

ゲート電流I101-Gが正の区間では、ソース電流I101-Sがドレイン電流I101-Dより大きくなっています。

これは、図のようにゲート電流IG3(I101-G)がドレイン電流I101-Dに加わりソース電流I101-Sになっていることを示しています。

つまり、ゲート電流が正の区間では、電流IG3(I101-G)がドレイン電流に加わりソース電流となります。

ゲート電流I101-Gが負の区間では、ソース電流I101-Sがドレイン電流I101-Dより小さくなっています。

これは、図のようにゲート電流IG4(I101-G)をドレイン電流I101-Dから差し引いたものがソース電流I101-Sになっていることを示しています。

つまり、ゲート電流が負の区間では、電流IG4(I101-G)とソース電流I101-Sはドレイン電流I101-Dから供給されています。

ゲート電流が負の区間でドレイン電流I101-Dが0まで下がらず(I102-Dよりも2倍大きな)ピークが現れています。

この回路は正負各2段のmosFETで構成されていますが、更に段数が多い場合、正側では高圧電源側に近いmosFETほど、そのピークが大きくなります。

負側のQ201も同様です。