高電圧増幅器

出力の保護

DUTに高電圧を印加したとき、そのDUTがショートモードで破壊すると高電圧

増幅器の出力からショートした瞬間に大電流が流れて高電圧増幅器にダメージ

を与えかねません

高電圧出力中にDUTが破壊された場合でも高電圧増幅器が保護される

ための回路を検討します

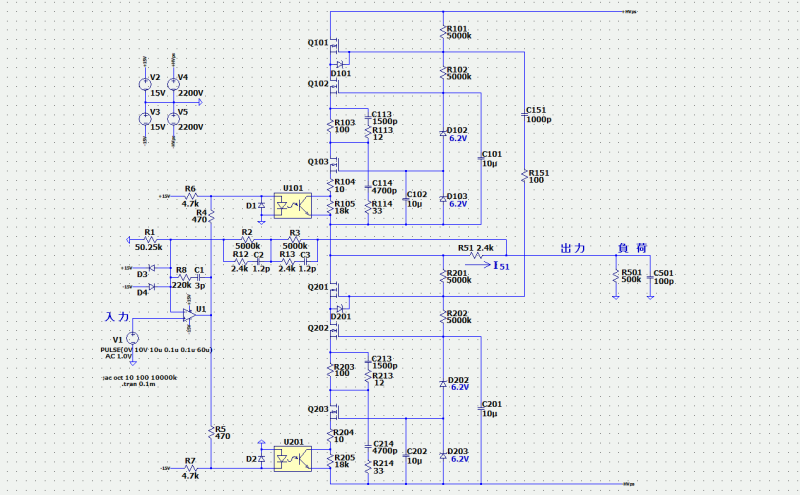

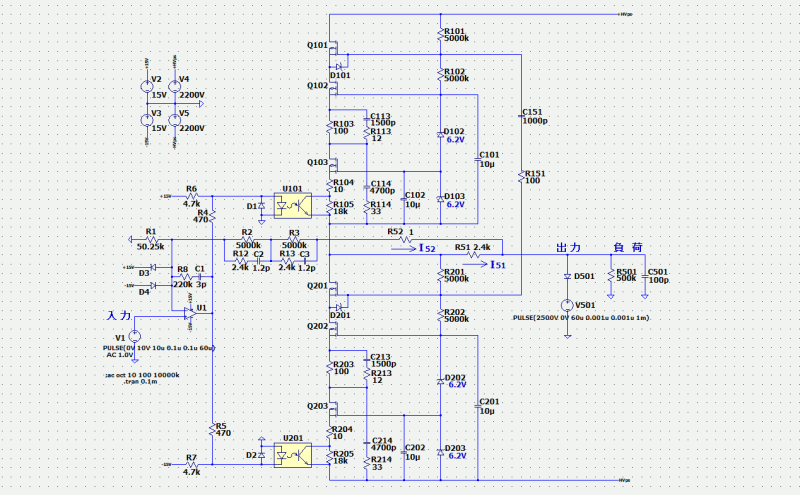

Fig 56-1

2.4kΩの抵抗R51、R12、R13をを入れて出力短絡時に高電圧増幅器を保護しています。

抵抗R51はBoosterAmp部を保護し、抵抗R12、R13(とダイオードD3,D4)は帰還回路から低圧回路部を保護します。

抵抗R3とコンデンサC3は、抵抗R51の負荷側に接続し、R51による電圧低下がゲインに影しないようします。

抵抗R51はBoosterAmp部を保護し、抵抗R12、R13(とダイオードD3,D4)は帰還回路から低圧回路部を保護します。

抵抗R3とコンデンサC3は、抵抗R51の負荷側に接続し、R51による電圧低下がゲインに影しないようします。

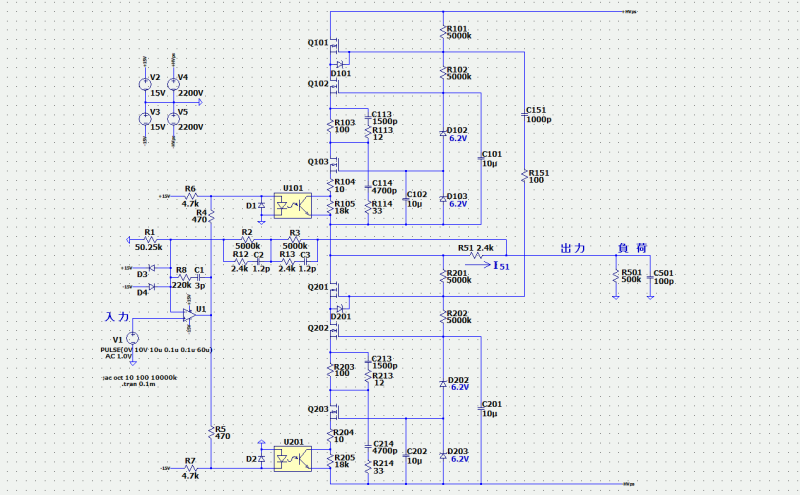

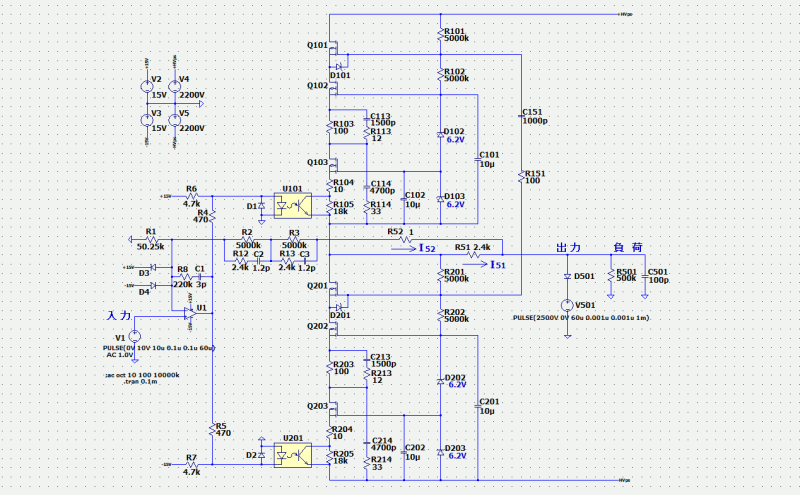

Fig 56-2

青 :出力電圧

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力電圧、保護抵抗R51に流れるの電流I51の応答波形です。

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力電圧、保護抵抗R51に流れるの電流I51の応答波形です。

Fig 56-3

電源V501を使用して出力を強制的に0Vに短絡(DUTのショートモードの破壊)することを模擬しています。

2kVの高圧が出力されてから50uS後(t=60uS)に出力を0V(厳密にはダイオードD501の順方向電圧分だけ残る)に落とします。

2kVの高圧が出力されてから50uS後(t=60uS)に出力を0V(厳密にはダイオードD501の順方向電圧分だけ残る)に落とします。

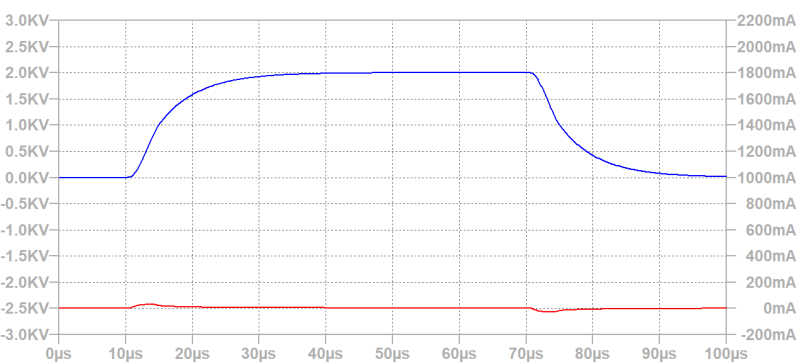

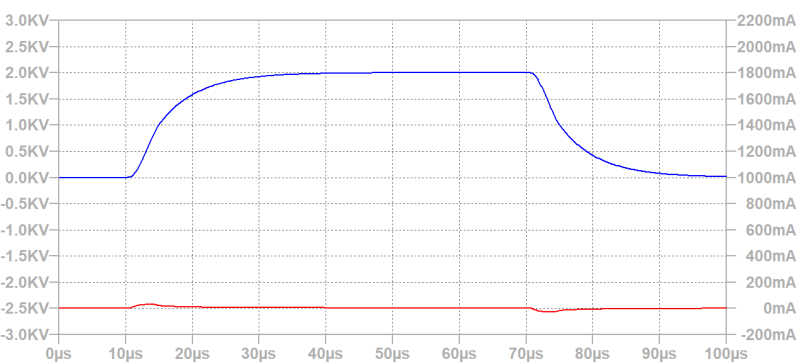

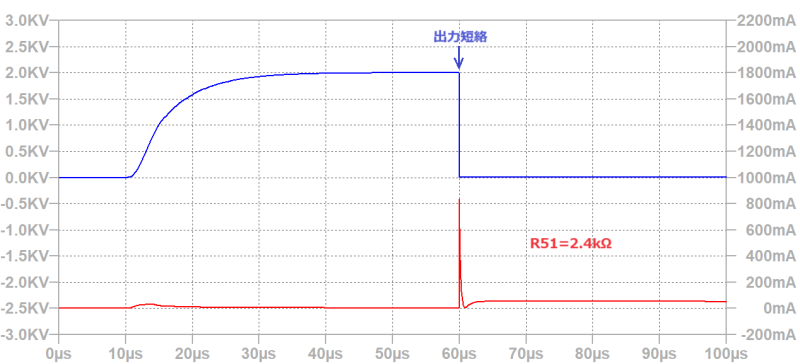

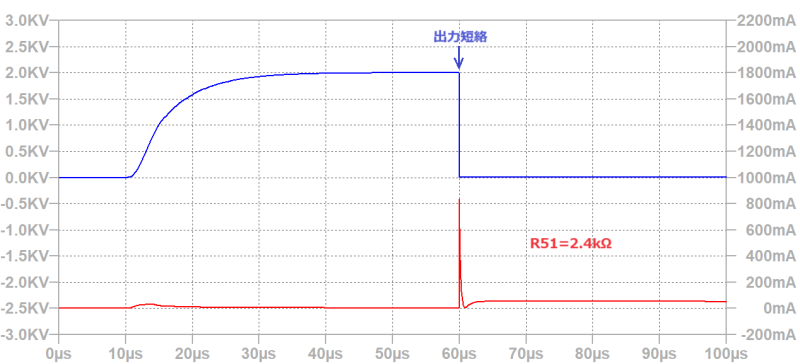

Fig 56-4

青 :出力電圧

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力電圧、2.4kΩの保護抵抗R51に流れるの電流I51の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が1A以下(約850mA、パルス幅1uS)に制限されています。

パルス幅1uS、1Aのサージ電流に耐えられるように設計(部品を選定)すれば、高電圧増幅器は壊れることなく保護されます。

尚、この保護抵抗R51の値は高圧電源の大きさに応じて、例えば5kVであればR51を5kΩ程度に大きくする必要があります。

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力電圧、2.4kΩの保護抵抗R51に流れるの電流I51の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が1A以下(約850mA、パルス幅1uS)に制限されています。

パルス幅1uS、1Aのサージ電流に耐えられるように設計(部品を選定)すれば、高電圧増幅器は壊れることなく保護されます。

尚、この保護抵抗R51の値は高圧電源の大きさに応じて、例えば5kVであればR51を5kΩ程度に大きくする必要があります。

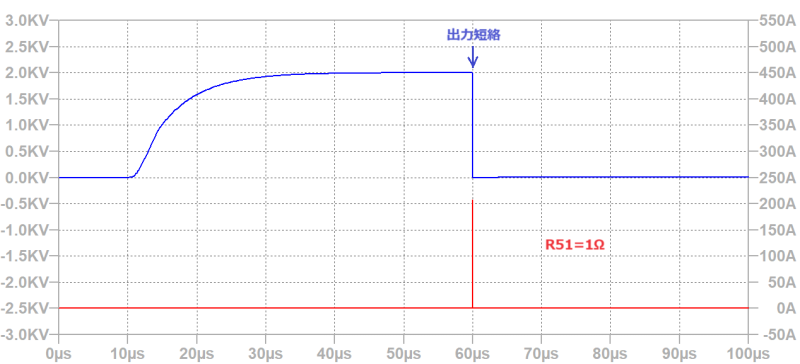

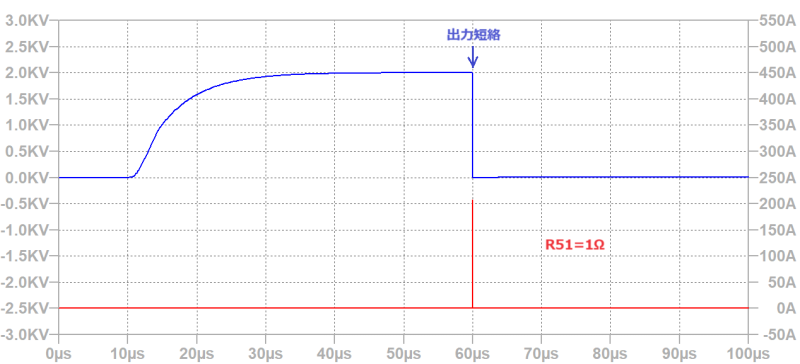

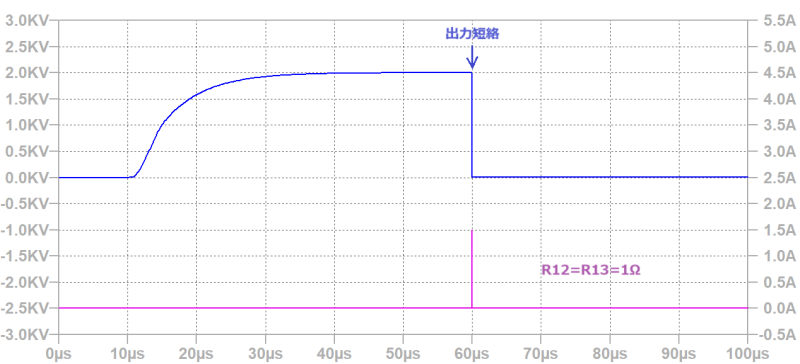

Fig 56-5

青 :出力電圧

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、1Ωの抵抗R51に流れるの電流I51の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が約210A流れています。

保護抵抗R51が無ければ、このような大電流によって高電圧増幅器にダメージを与え、最悪の場合は破壊されることになります。

赤 :抵抗R51の電流 I51

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、1Ωの抵抗R51に流れるの電流I51の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が約210A流れています。

保護抵抗R51が無ければ、このような大電流によって高電圧増幅器にダメージを与え、最悪の場合は破壊されることになります。

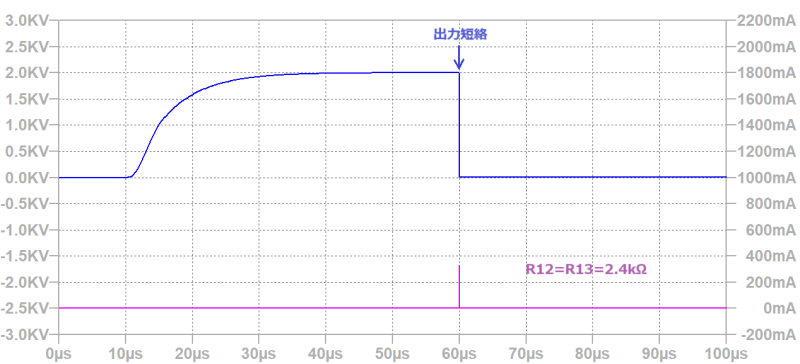

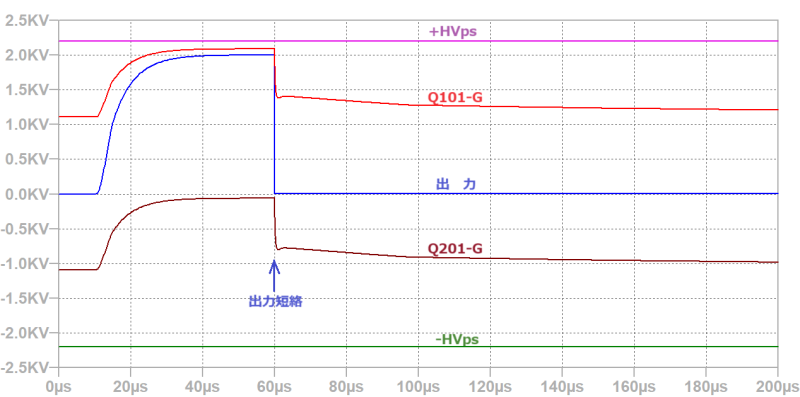

Fig 56-6

青 :出力電圧

紫 :抵抗R52の電流 I52

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、保護抵抗R12=R13=2.4kΩのときの抵抗R52に流れる電流I52の応答波形です。

出力短絡時、帰還回路R2、R3、C2、C3に流れる電流I52が約350mA(パルス幅1uS)に制限されています。

パルス幅1uS、400mAのサージ電流に耐えられるように設計(部品を選定)すれば、高電圧増幅器は壊れることなく保護されます。

紫 :抵抗R52の電流 I52

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、保護抵抗R12=R13=2.4kΩのときの抵抗R52に流れる電流I52の応答波形です。

出力短絡時、帰還回路R2、R3、C2、C3に流れる電流I52が約350mA(パルス幅1uS)に制限されています。

パルス幅1uS、400mAのサージ電流に耐えられるように設計(部品を選定)すれば、高電圧増幅器は壊れることなく保護されます。

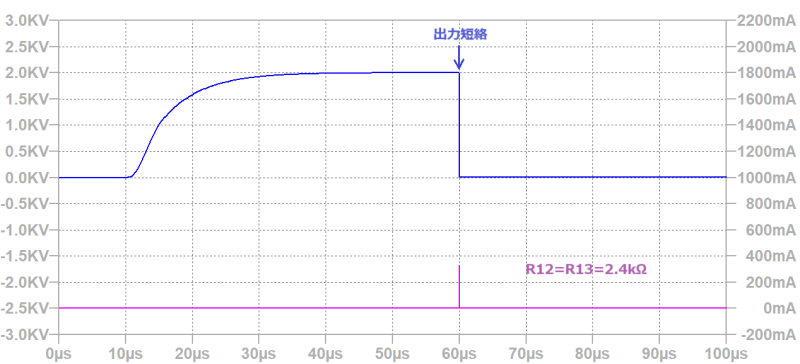

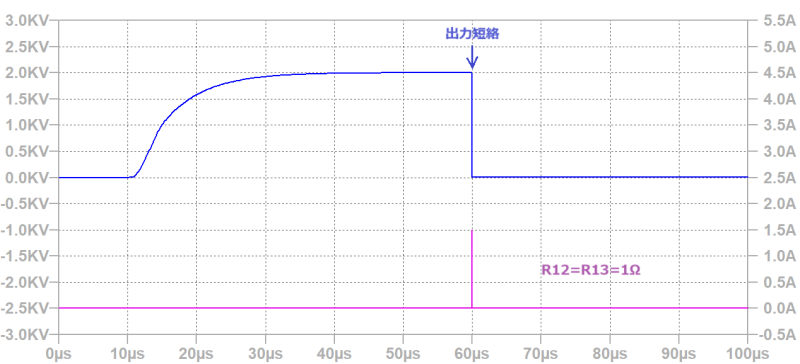

Fig 56-7

青 :出力電圧

紫 :抵抗R52の電流 I52

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、R12=R13=1Ωのときの抵抗R52に流れる電流I52の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が約1.5A流れています。

2.4kΩの保護抵抗R12、R13が無ければ、このような大きな電流によって高電圧増幅器にダメージを与え、最悪の場合は破壊されることになります。

紫 :抵抗R52の電流 I52

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、R12=R13=1Ωのときの抵抗R52に流れる電流I52の応答波形です。

出力短絡時、高電圧増幅器の出力電流I51が約1.5A流れています。

2.4kΩの保護抵抗R12、R13が無ければ、このような大きな電流によって高電圧増幅器にダメージを与え、最悪の場合は破壊されることになります。

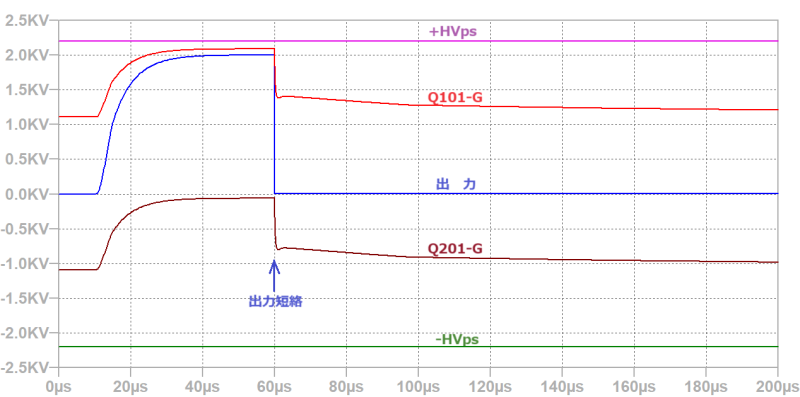

Fig 56-8

Q101-G:Q101のゲート波形 Q201-G:Q201のゲート波形

+HVps :+2200V高圧電源 -HVps :-2200V高圧電源

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、出力、Q101のゲート、Q102のゲートの応答波形です。

出力が短絡したt=60uS以降でもQ101とQ201のゲート間の電位差はGBコンデンサC151によってほぼ一定に保たれています。

(Q101のゲート − 出力)と(高圧電源+HVps − Q101のゲート)の電位差は、出力が短絡したt=60uS以降に多少バランスを崩していますが

(mosFETの耐圧を超える)問題となるような大きな崩れではなく、速やかに電位差が等しくなる方向に向かっています。

出力と負側のQ201のゲート、-HVpsとの関係も同様です。

+HVps :+2200V高圧電源 -HVps :-2200V高圧電源

0V/+10V、60uSパルス入力に対する出力をt=60uSで短絡した、出力、Q101のゲート、Q102のゲートの応答波形です。

出力が短絡したt=60uS以降でもQ101とQ201のゲート間の電位差はGBコンデンサC151によってほぼ一定に保たれています。

(Q101のゲート − 出力)と(高圧電源+HVps − Q101のゲート)の電位差は、出力が短絡したt=60uS以降に多少バランスを崩していますが

(mosFETの耐圧を超える)問題となるような大きな崩れではなく、速やかに電位差が等しくなる方向に向かっています。

出力と負側のQ201のゲート、-HVpsとの関係も同様です。

-2kVの負電圧出力時も電圧や電流の方向が変わるだけで、ほぼ同様に回路は保護されます。