高電圧増幅器

電圧バランスの微調整

ブースターアンプを構成する多段mosFETの電圧バランスを調整、検討します

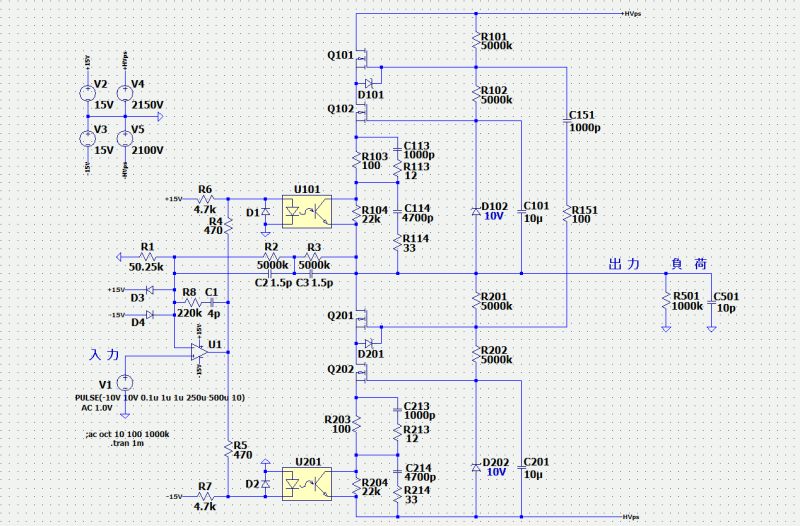

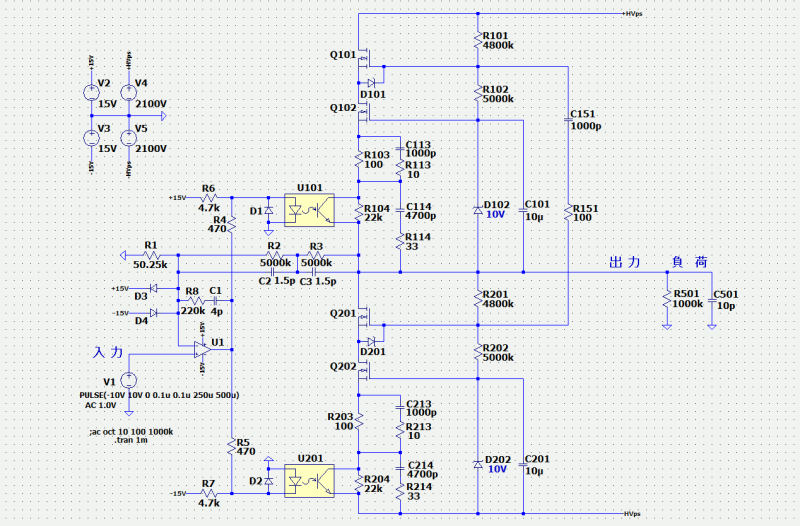

Fig 44-1

正高圧電源を50V高い2150Vに上げて、+2000V最大出力時にその出力電圧とQ101の電位差に余裕を持たせます。

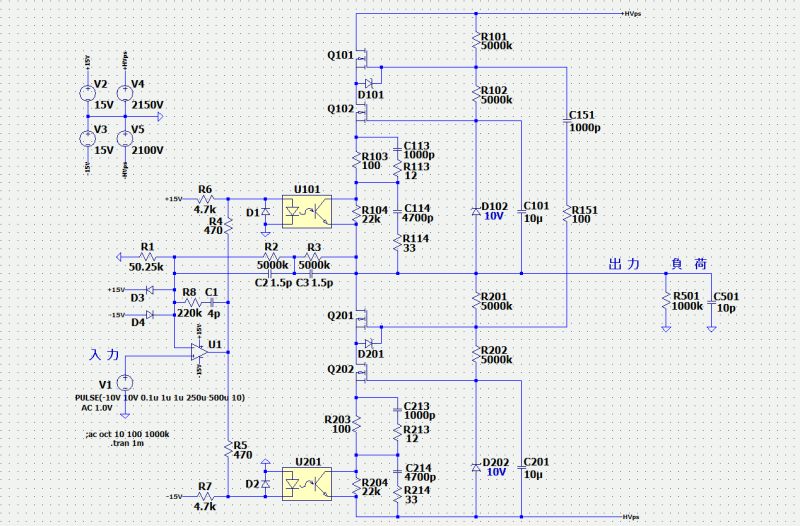

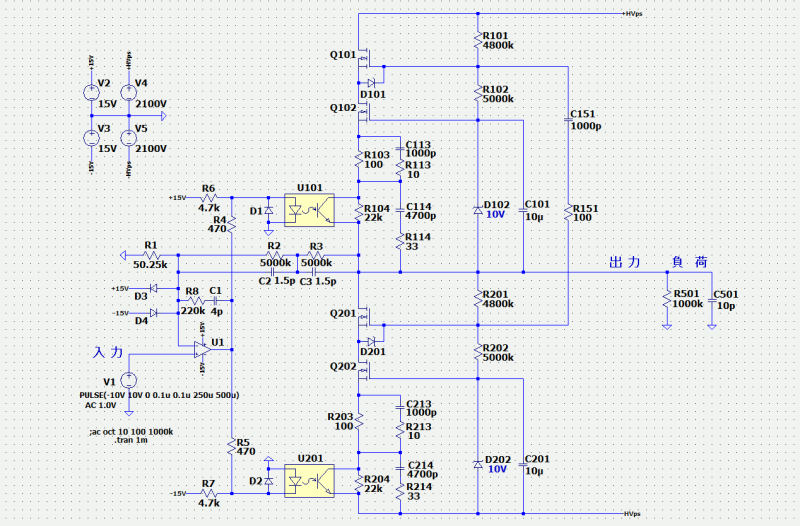

Fig 44-2

Q101-G:Q101のゲート波形 Q201-G:Q201のゲート波形

+HVps :+2150V高圧電源 -HVps :-2100V高圧電源

2kHz、±10Vpkパルス入力に対する±2kVpk出力波形です。

Fig43-4のパルス波形に比べて、+2000V出力時の出力とQ101-Gとの電位差が大きくなり少し余裕が出ています。

+HVps :+2150V高圧電源 -HVps :-2100V高圧電源

2kHz、±10Vpkパルス入力に対する±2kVpk出力波形です。

Fig43-4のパルス波形に比べて、+2000V出力時の出力とQ101-Gとの電位差が大きくなり少し余裕が出ています。

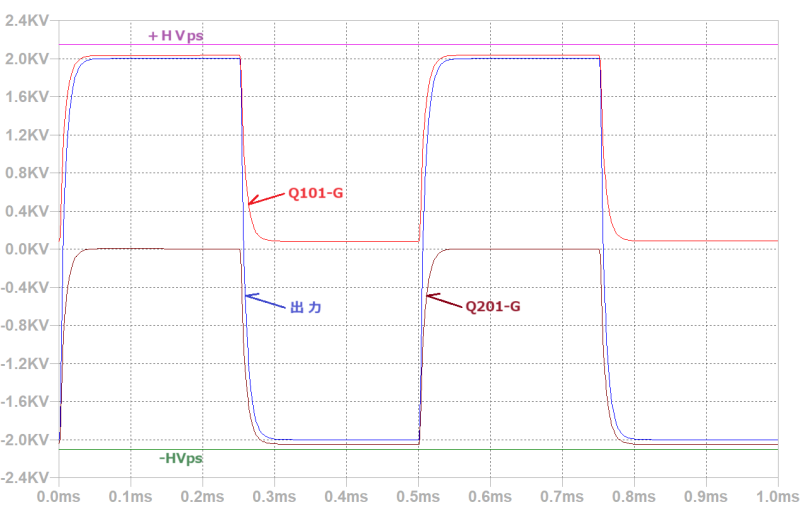

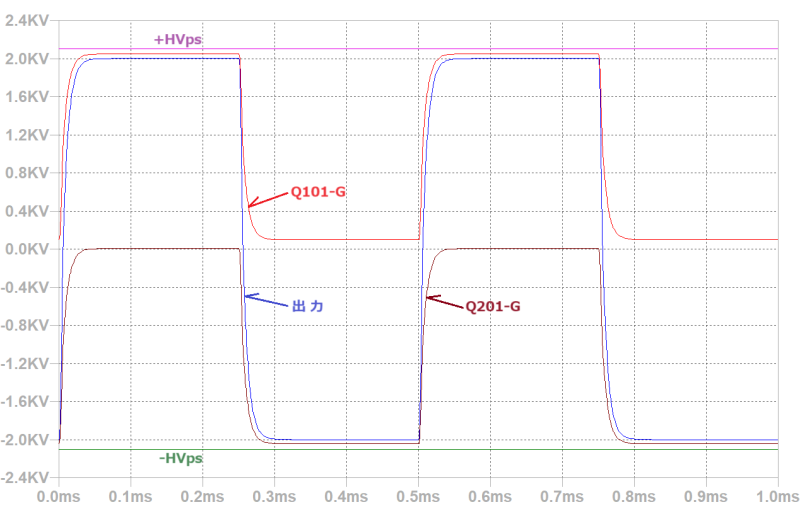

Fig 44-3

抵抗R101、R201を5MΩのR102、R202より小さな4.8MΩに下げて、+2000V最大出力時にその出力電圧とQ101の電位差に余裕を持たせます。

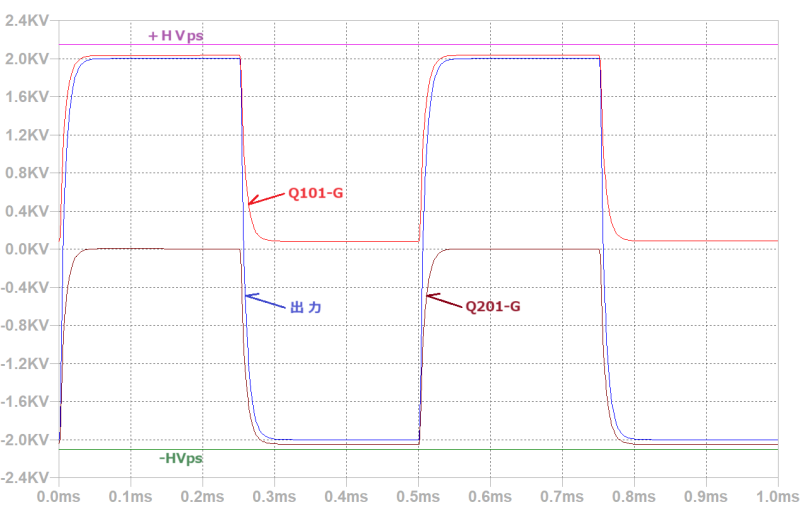

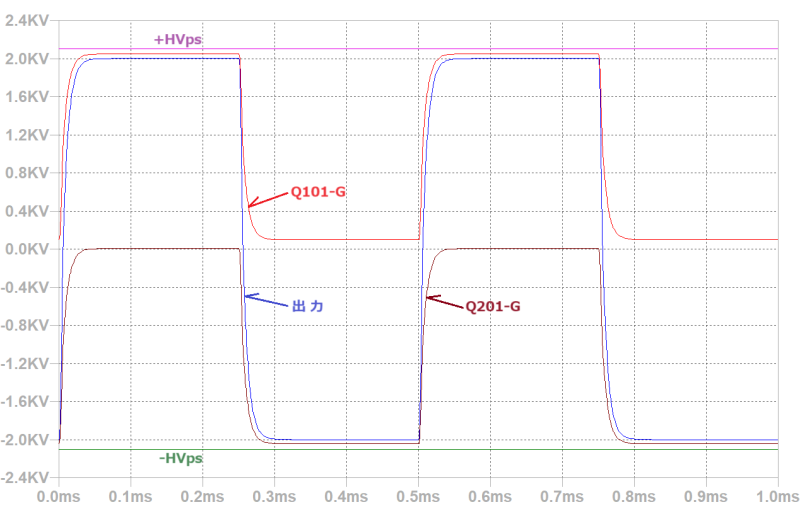

Fig 44-4

Q101-G:Q101のゲート波形 Q201-G:Q201のゲート波形

+HVps :+2100V高圧電源 -HVps :-2100V高圧電源

2kHz、±10Vpkパルス入力に対する±2kVpk出力波形です。

正の高圧電源+HVpsを+2150Vに上げなくても、+2000V出力時の出力とQ101-Gとの電位差に余裕があります。

+HVps :+2100V高圧電源 -HVps :-2100V高圧電源

2kHz、±10Vpkパルス入力に対する±2kVpk出力波形です。

正の高圧電源+HVpsを+2150Vに上げなくても、+2000V出力時の出力とQ101-Gとの電位差に余裕があります。